(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-212266

(P2008-212266A)

(43) 公開日 平成20年9月18日(2008.9.18)

| (51) Int.Cl.                | F 1          | テーマコード (参考) |

|-----------------------------|--------------|-------------|

| <b>A61B 1/04</b> (2006.01)  | A 61 B 1/04  | 2 H 04 0    |

| <b>G02B 23/24</b> (2006.01) | G 02 B 23/24 | 4 C 06 1    |

| <b>HO4N 7/18</b> (2006.01)  | H 04 N 7/18  | 5 C 05 4    |

|                             | H 04 N 7/18  | U           |

審査請求 未請求 請求項の数 6 O L (全 11 頁)

|           |                            |          |                                              |

|-----------|----------------------------|----------|----------------------------------------------|

| (21) 出願番号 | 特願2007-51157 (P2007-51157) | (71) 出願人 | 000113263<br>HO Y A 株式会社<br>東京都新宿区中落合2丁目7番5号 |

| (22) 出願日  | 平成19年3月1日 (2007.3.1)       | (74) 代理人 | 100090169<br>弁理士 松浦 孝                        |

|           |                            | (74) 代理人 | 100124497<br>弁理士 小倉 洋樹                       |

|           |                            | (74) 代理人 | 100127306<br>弁理士 野中 剛                        |

|           |                            | (74) 代理人 | 100129746<br>弁理士 虎山 滋郎                       |

|           |                            | (74) 代理人 | 100132045<br>弁理士 坪内 伸                        |

最終頁に続く

(54) 【発明の名称】マスク処理装置

## (57) 【要約】

【課題】画像のマスク処理において、マスク境界におけるジャギーによる影響を簡略な構成かつ高速な処理により低減する。

【解決手段】撮像素子からのアナログ画像信号に対して、映像信号部 S 1 の両側に第 1 のマスク処理を施し、第 1 マスク領域 M 1 の映像信号をペダスタルレベル L 1 とする。第 1 のマスク処理が施された画像信号に対して、第 1 マスク領域 M 1 がペダスタルレベル L 1 とされた映像信号の両側、第 1 マスク領域 M 1 の一画素内側の各画素に対して第 2 のマスク処理を施し、第 2 マスク領域 M 2 に対応する画素を所定のグレーレベル L 2 とする。

【選択図】図 4

**【特許請求の範囲】****【請求項 1】**

撮像素子からの画像信号に対してマスク処理を施すマスク処理装置であって、前記画像信号に対して相対的に濃い第1濃度の第1マスク領域を形成する第1マスク処理手段と、

前記第1マスク領域の周縁に隣接する所定の画素数分の領域の画素を、相対的に薄い第2濃度として第2マスク領域を形成する第2マスク処理手段とを備えることを特徴とするマスク処理装置。

**【請求項 2】**

前記第1マスク領域が水平ラインに対して斜めの境界線部を含み、前記第2マスク領域が前記境界線部に隣接して設けられることを特徴とする請求項1に記載のマスク処理装置。

**【請求項 3】**

前記第2マスク領域を構成する前記第1マスク領域の周縁に隣接する前記所定の画素数が1画素であることを特徴とする請求項1に記載のマスク処理装置。

**【請求項 4】**

前記第1濃度が画像信号の黒レベルであり、前記第2濃度が所定のグレーレベルであることを特徴とする請求項1に記載のマスク処理装置。

**【請求項 5】**

前記第1マスク領域が、画像の周縁部を取り囲む領域であり、前記第2マスク領域が、前記第1マスク領域の内側周縁部に沿った領域であることを特徴とする請求項1に記載のマスク処理装置。

**【請求項 6】**

請求項1乃至請求項5の何れか一項に記載のマスク処理装置を用いて、電子内視鏡で撮影された画像にマスク処理を施す電子内視鏡装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、画像信号に対して電子マスク処理を施す装置、およびそれを用いた電子内視鏡装置に関する。

**【背景技術】****【0002】**

撮像素子の周縁部には、物理的に遮光された光学マスク領域が設けられ、この領域から出力される画像信号に対しては更に電子マスク処理が施される。また、電子内視鏡などにおいては、光学マスク領域に囲まれる撮像領域から出力される画像信号に対しても、例えばピントがっていない周縁領域に対して電子マスク処理が施される（特許文献1参照）。

【特許文献1】特開2003-325444号公報

**【発明の開示】****【発明が解決しようとする課題】****【0003】**

しかし、従来の電子マスク処理は、ある画素に対してマスクを施すか、施さないかの2値的な処理により行われるため、マスク領域境界に曲線や水平ラインに対して斜めの直線を用いると、これらの部分にジャギーが発生し見栄えが悪いと言う問題がある。

**【0004】**

本発明は、画像のマスク処理において、マスク境界におけるジャギーによる影響を簡略な構成かつ高速な処理により低減することを目的としている。

**【課題を解決するための手段】****【0005】**

本発明のマスク処理装置は、撮像素子からの画像信号に対してマスク処理を施すマスク

10

20

30

40

50

処理装置であって、画像信号に対して相対的に濃い第1濃度の第1マスク領域を形成する第1マスク処理手段と、第1マスク領域の周縁に隣接する所定の画素数分の領域の画素を、相対的に薄い第2濃度として第2マスク領域を形成する第2マスク処理手段とを備えたことを特徴としている。

【0006】

第1マスク領域は、水平ラインに対して斜めの境界線部を含み、第2マスク領域はこの境界線部に隣接して設けられる。第2マスク領域を構成する第1マスク領域の周縁に隣接する所定の画素数は1画素であることが好ましい。第1濃度は例えば画像信号の黒レベルであり、第2濃度は所定のグレーレベルである。第1マスク領域は、画像の周縁部を取り囲む領域であり、第2マスク領域は、第1マスク領域の内側周縁部に沿った領域である。

10

【0007】

また、本発明の電子内視鏡装置は、上記マスク処理装置を用いて電子内視鏡で撮影された画像にマスク処理を施すことを特徴としている。

【発明の効果】

【0008】

以上のように、本発明によれば、画像のマスク処理において、マスク境界におけるジャギーによる影響を簡略な構成かつ高速な処理により低減することができる。

【発明を実施するための最良の形態】

【0009】

以下、本発明の実施の形態を、図面を参照して説明する。

20

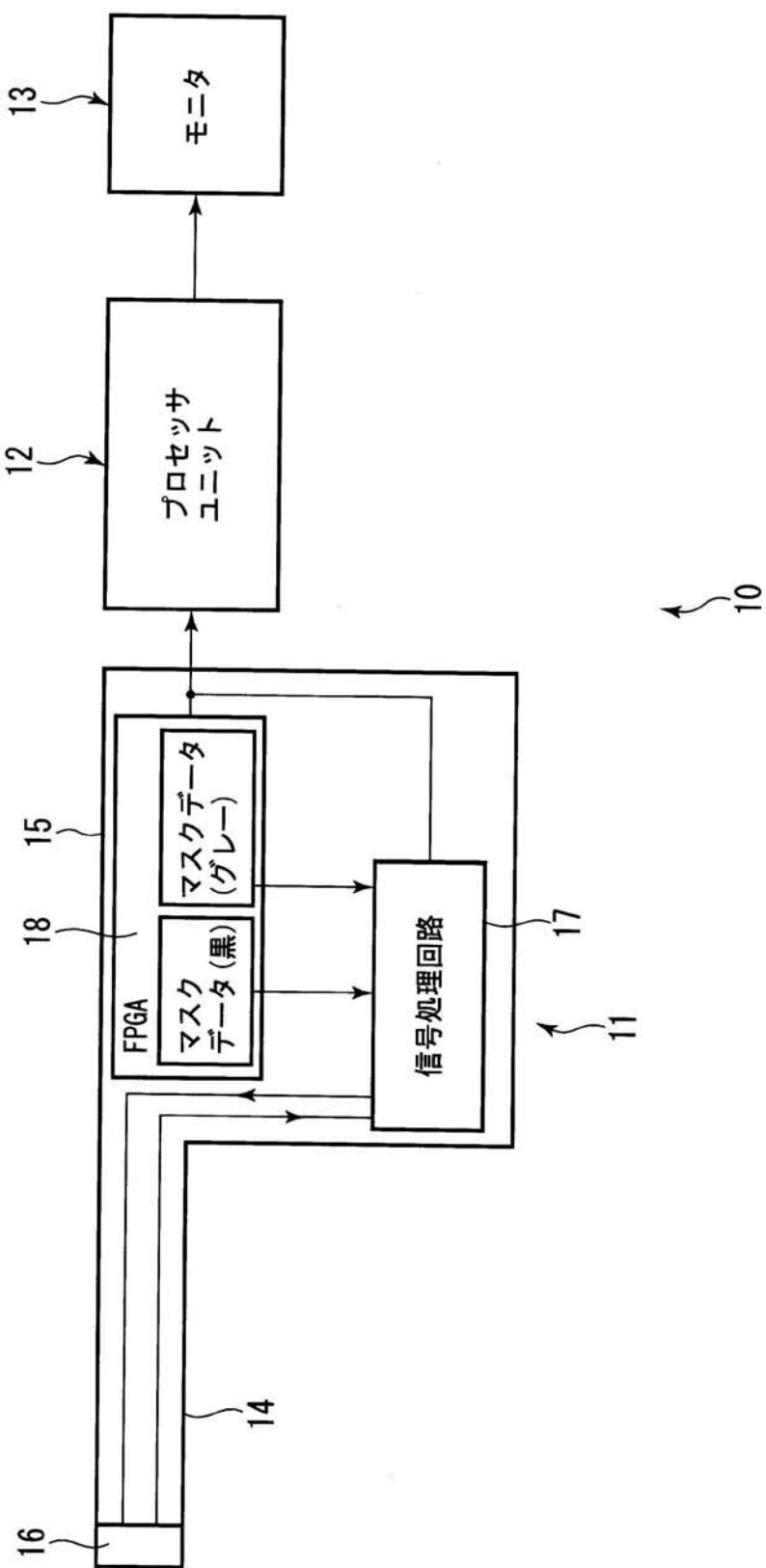

図1は、本発明の一実施形態である電子内視鏡システムの構成を模式的に示すプロック図である。

【0010】

電子内視鏡システム10は、管腔内に挿入される電子スコープ11と、電子スコープ11に照明光を供給するとともに電子スコープ11からの画像信号を処理するプロセッサユニット12と、電子スコープ11で撮影された内視鏡画像を表示するモニタ13から主に構成される。

【0011】

電子スコープ11は、従来周知のように可撓性を有する管状の挿入部14と、挿入部14が連結され、操作者が保持して各種操作を行う操作部15とを備える。また、操作部15は可撓管およびコネクタを介してプロセッサユニット12に着脱自在に装着され、電気的、光学的にプロセッサユニット12に接続される。

30

【0012】

挿入部14の先端には、CCDなどの撮像素子16が設けられ、撮像素子16からの画像信号は、操作部15に設けられた信号処理回路17を介してデジタル信号に変換され、プロセッサユニット12へと出力される。プロセッサユニット12では、画像信号に対して従来周知の所定の信号処理が施され、例えば所定の規格の映像信号に変換されてモニタ13へと出力される。

【0013】

また操作部15には、FPGAなどを用いたマスク回路18が設けられ、マスク回路18では、所定のマスクデータが保存、または生成される。マスク回路18からのマスク信号は、信号処理回路17へと送られ、撮像素子16からの画像信号に重畠され、これにより電子マスク処理が施される。本実施形態では、後述するように2種類のマスクデータ(第1および第2のマスクデータ)が用いられ、マスク回路18から信号処理回路17へと出力される。

40

【0014】

なお、従来周知のように、電子スコープ11には、図示しないライトガイドが配設され、その一端はプロセッサユニット12内に設けられた光源と接続され、光源からの光はライトガイドを介して挿入部14の先端から管腔内へと照射される。また、撮像素子16は、操作部15内に設けられた撮像素子駆動回路(不図示)により駆動制御されるが、本実

50

施形態では、撮像素子駆動回路は便宜的に信号処理回路 17 の一部として描かれている。

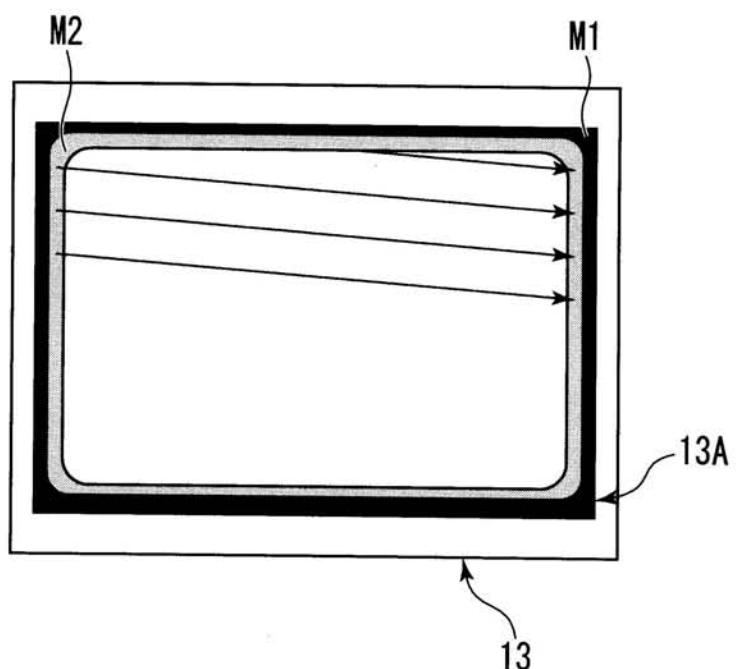

【0015】

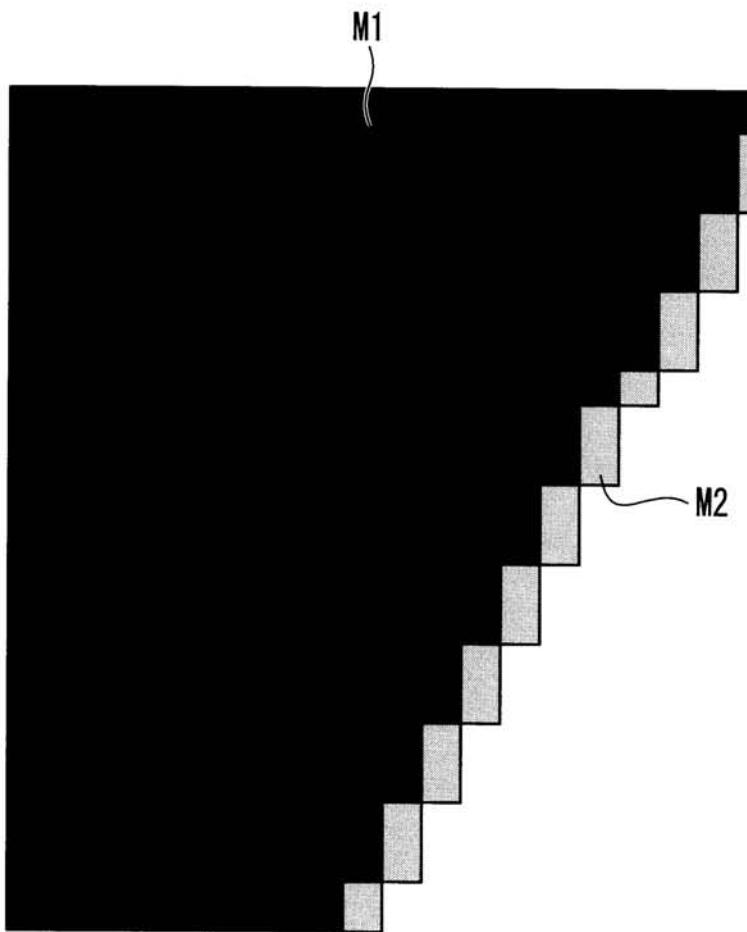

図 2 に、本実施形態のマスク処理が施され、モニタ 13 の画面 13A に表示される画像の一例を模式的に示す。画面 13A の周縁部には、第 1 のマスクデータにより第 1 マスク領域 M1 が形成され、第 1 マスク領域の内側には、第 2 のマスクデータにより第 2 マスク領域 M2 が形成される。第 1 マスク領域では、その領域の画素が黒レベル（第 1 濃度）とされ、第 2 マスク領域では、その領域の画素が黒レベルよりも薄い（明るい）濃度のグレーレベル（第 2 濃度）とされる。

【0016】

図 2 において第 2 マスク領域 M2 は誇張されて描かれているが、第 2 マスク領域 M2 は、例えば第 1 マスク領域 M1 の内側周縁部に沿って隣接する 1 画素分内側の画素からなる。また、本実施形態において、第 1 および第 2 マスク領域 M1、M2 の四隅は弧状曲線とされる。

10

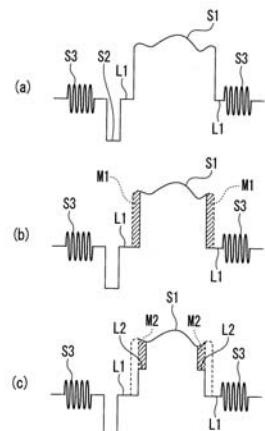

【0017】

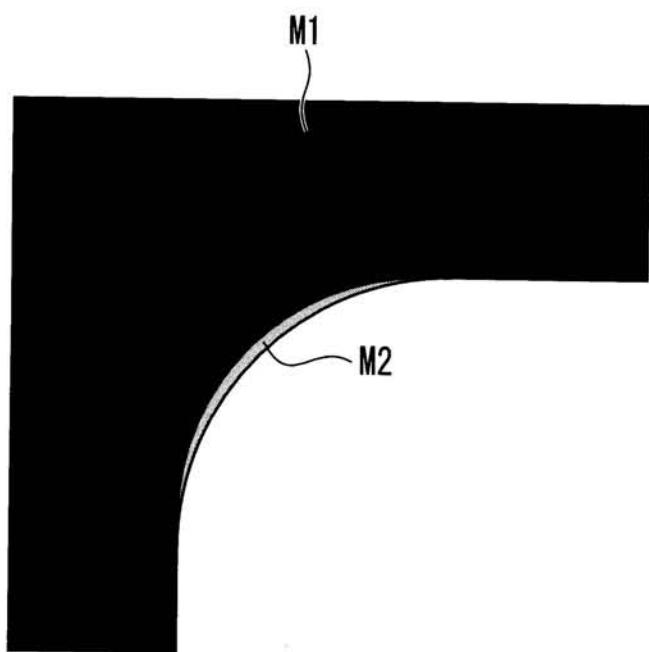

図 3 に、弧状曲線とされた第 1 および第 2 マスク領域 M1、M2 の左上角部の拡大図を示す。図示されるように、第 1 マスク領域 M1 は、黒レベルのマスクであり、曲線部（斜めの直線であっても同様）においてジャギーが発生する。第 2 マスク領域 M2 は、グレーレベルのマスクであり、図示されるように、第 1 マスク領域 M1 の境界から水平方向内側へ、例えば一画素分形成される。すなわち、第 2 マスク領域 M2 は、水平走査による画面 13A への描画において、各水平ラインにおける第 1 マスク領域 M1 の左右の内側境界画素に隣接した 1 画素をグレーレベルとすることにより形成される。

20

【0018】

なお、本実施形態では、第 1 マスク領域 M1 の全周に沿った内側 1 画素分を第 2 マスク領域 M2 とするため、第 1 マスク領域 M1 が形成する上辺下側に隣接する 1 水平ラインと下辺上側に隣接する 1 水平ラインも第 2 マスク領域 M2 とされる。

30

【0019】

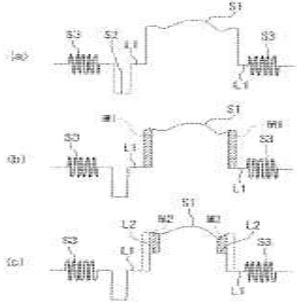

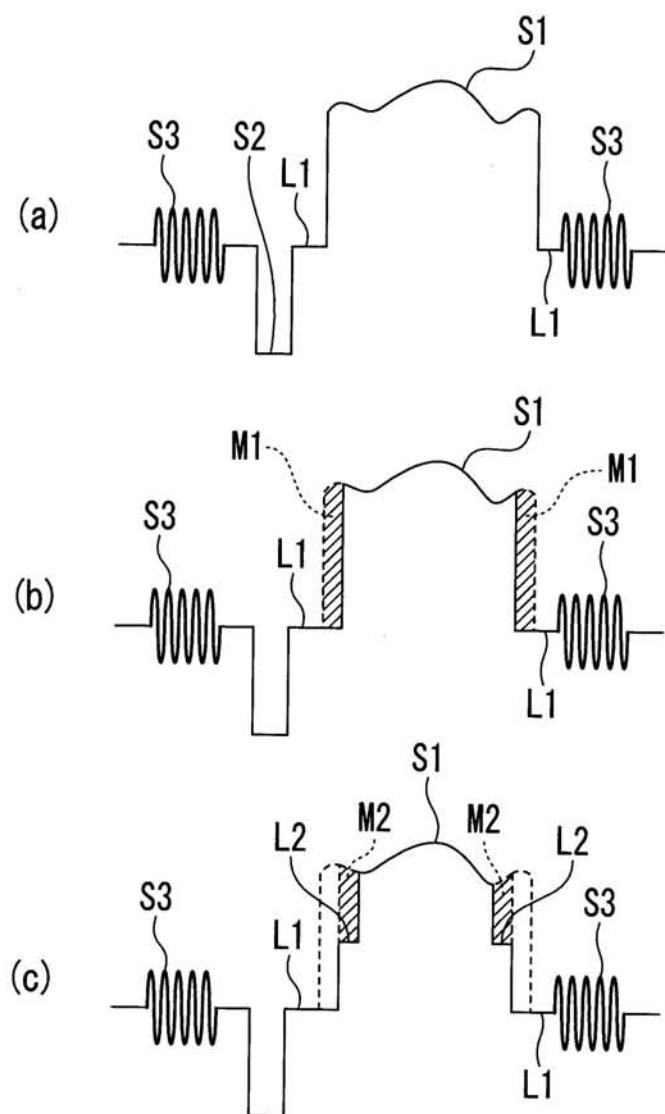

図 4 に、本実施形態におけるマスク処理の原理を模式的に示す。図 4 (a) は、撮像素子 16 からの信号処理回路 17 に入力される 1 水平ライン分のアナログ画像信号の一例である。なお、本実施形態において以下の処理は、例えばマスク回路 18 (図 1 参照) によるタイミング制御により、信号処理回路 17 において実行される。また、図 4 (a) において、信号部 S1 は映像信号部であり、信号部 S2 は水平同期信号部、信号部 S3 はカラーバースト信号部である。また、信号レベル L1 は黒レベルを決定するペダスタルレベルである。

30

【0020】

図 4 (b) は、図 4 (a) の画像信号に第 1 のマスク処理を施した 1 水平ライン分のアナログ画像信号の一例である。すなわち、図 4 (b) において斜線が施された領域（水平ラインの両端に対応）の映像信号が、第 1 のマスク処理によりペダスタルレベル L1 とされる。なお、これは図 4 (a) の画像信号に対して、斜線部に対応する区間、画像信号レベルをペダスタルレベル L1 とすることにより達成される。

40

【0021】

図 4 (c) は、図 4 (b) において第 1 のマスク処理が施された画像信号に対して、本実施形態の第 2 のマスク処理を施した 1 水平ライン分のアナログ画像信号の一例である。図 4 (c) では、図 4 (b) において、ペダスタルレベル L1 とされた、第 1 マスク領域 M1 の内側の例えば両側 1 画素分の映像信号に対して第 2 のマスク処理が施される。すなわち、斜線が施された領域の映像信号が、グレーレベル L2 (ペダスタルレベルと映像信号の最大値との間の所定レベル (例えば中間値)) の信号とされる。なお、第 2 のマスク処理は、図 4 (b) の画像信号に対し、斜線部に対応する区間、画像信号レベルをグレーレベル L2 とすることにより達成される。

【0022】

以上のように、本実施形態によれば、電子内視鏡画像に対して簡略な構成で高速にマス

50

ク処理を施しつつ、マスク領域角分などのジャギーを目立たなくすることができる。特に、本実施形態では、アナログ信号に対して、第1、第2マスク領域に対応する所定区間、信号レベルを所定レベルに維持するだけの簡略な構成で、高速にジャギーを低減したマスク処理を施すことができる。このような回路は電子スコープ側に設けることが容易であるため、本実施形態の構成を採用することにより、電子スコープ側でジャギーを低減したマスク処理を施すことができる。これにより様々な電子スコープが装着されるプロセッサユニット側でマスク処理を行う必要がないため、プロセッサユニットが、装着された電子スコープの型を認識し、これに対応したマスク処理を施すためのデータ等を保持する必要がない。

## 【0023】

10

なお、本実施形態の場合、ジャギーが発生するのは、境界線が弧状曲線となるマスク領域の4隅のみであるので、図5に示すように、ジャギー発生部のみに対して第2マスク領域M2'を設ける構成としてもよい。

## 【0024】

なお本発明は、マスク領域の境界におけるジャギー発生箇所に同様に適用できるものであって、マスク領域の角分が弧状曲線とされた本実施形態の他、斜めの直線を含む境界などにおいても適用可能である。また、本実施形態では、2段階のレベルのマスクを用いてマスク処理を行ったが、第2マスク領域の更に内側に、更に薄いグレーの領域を1重または複数設けることも可能である。

## 【0025】

20

また、本実施形態では、グレースケールを用いたが、マスクの色はグレーに限定されるものではなく、青など特定の色の複数のレベルのマスク領域を設ける構成としてもよい。

## 【0026】

更に、本実施形態では、アナログ信号に対してマスク処理を施したが、画像信号をデジタル信号に変換した後、第1マスク領域の内側の画素に対して第2のマスク処理を施すことも可能である。また、本実施形態においては、第2マスク領域は1画素分としたが1画素分以上であってもよい。

## 【図面の簡単な説明】

## 【0027】

30

【図1】本発明の一実施形態である電子内視鏡システムの構成を示すブロック図である。

【図2】本実施形態におけるマスク画像の一例である。

【図3】図2のマスク画像の左上角分を拡大した図である。

【図4】アナログ画像信号に対して施される第1及び第2マスク処理の原理を示す図である。

【図5】マスク画像の変形例における左上角部の拡大図である。

## 【符号の説明】

## 【0028】

40

10 電子内視鏡システム

11 電子スコープ

12 プロセッサユニット

13 モニタ

16 撮像素子

17 信号処理回路

18 マスク回路

M1 第1マスク領域

M2 第2マスク領域

L1 ペダスタルレベル

L2 グレーレベル

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 森 智洋

東京都板橋区前野町2丁目36番9号 ペンタックス株式会社内

Fターム(参考) 2H040 GA02 GA06 GA11

4C061 AA00 BB01 CC06 DD03 JJ17 NN05 SS21 WW04

5C054 CC07 EA05 FE00 FE06 HA12

|                |                                                                                                                                                                                                                                                                         |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 掩模处理装置                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2008212266A</a>                                                                                                                                                                                                                                           | 公开(公告)日 | 2008-09-18 |

| 申请号            | JP2007051157                                                                                                                                                                                                                                                            | 申请日     | 2007-03-01 |

| [标]申请(专利权)人(译) | 保谷股份有限公司                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | HOYA株式会社                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 森智洋                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 森 智洋                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | A61B1/04 G02B23/24 H04N7/18                                                                                                                                                                                                                                             |         |            |

| FI分类号          | A61B1/04.370 G02B23/24.B H04N7/18.M H04N7/18.U A61B1/04 A61B1/045.611                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 2H040/GA02 2H040/GA06 2H040/GA11 4C061/AA00 4C061/BB01 4C061/CC06 4C061/DD03 4C061/JJ17 4C061/NN05 4C061/SS21 4C061/WW04 5C054/CC07 5C054/EA05 5C054/FE00 5C054/FE06 5C054/HA12 4C161/AA00 4C161/BB01 4C161/CC06 4C161/DD03 4C161/JJ17 4C161/NN05 4C161/SS21 4C161/WW04 |         |            |

| 代理人(译)         | 松浦 孝<br>野刚                                                                                                                                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                               |         |            |

## 摘要(译)

要解决的问题：通过简单的构造和图像掩蔽过程中的高速处理来减少锯齿对掩蔽边界的影响。解决方案：该掩蔽装置对来自图像信号部分S1两侧的图像拾取装置的模拟图像信号执行第一掩模处理，并将第一掩蔽区域M1的图像信号定义为基座级L1。该掩模装置对通过第一掩模处理对图像信号两侧的每个像素处理的图像信号执行第二掩模处理，其中第一掩模区域M1被定义为基座级别L1并且在第一掩模的一个基座内部区域M1，将与第二掩蔽区域M1对应的像素定义为规定的灰度级L2。 ↴